FPGA入门教程(1):点灯大师

介绍

FPGA的全称为 Field-Programmable Gate Array,即现场可编程门列阵。 FPGA 是在 PAL、 GAL、 CPLD 等可编程器件的基础上进一步发展的产物, 是作为专用集成电路( ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 简而言之, FPGA 就是一个可以通过编程来改变内部结构的芯片。

目前应用到六大领域:通信领域、数字信号处理领域、视频图像处理领域、高速接口设计领域、人工智能领域、IC验证领域。

详情请看 (FPGA简介)[https://zhuanlan.zhihu.com/p/401954780]

需要学习的知识点有 数电、verilog语言等知识点。

环境安装

关于quartus ii、Modelsim等软件的安装,请自行搜索安装哈。

开发流程

本质就是写一套硬件描述语言,能够在指定的硬件平台上实现相应的功能。

流程如下

设计定义 具体的开发任务,比如让LED一秒闪烁一次

设计输入 编写逻辑(使用verilog代码描述逻辑),画逻辑图,使用IP核等

分析综合 使用专业的EDA软件(Quartus、Vivado)进行 对所写的逻辑描述内容进行分析,并得到逻辑门级别的电路内容。

功能仿真 使用专门的仿真工具进行仿真,验证设计的逻辑功能是否能够实现。

布局布线

分析性能 通过时序仿真、静态时序分析等方法分析性能。

下载到目标板上运行,查看运行结果

点亮第一个LED

本人使用的板子为 某鱼上淘的 小梅哥AC620。

新建工程

首先打开quartus ii,新建一个工程。

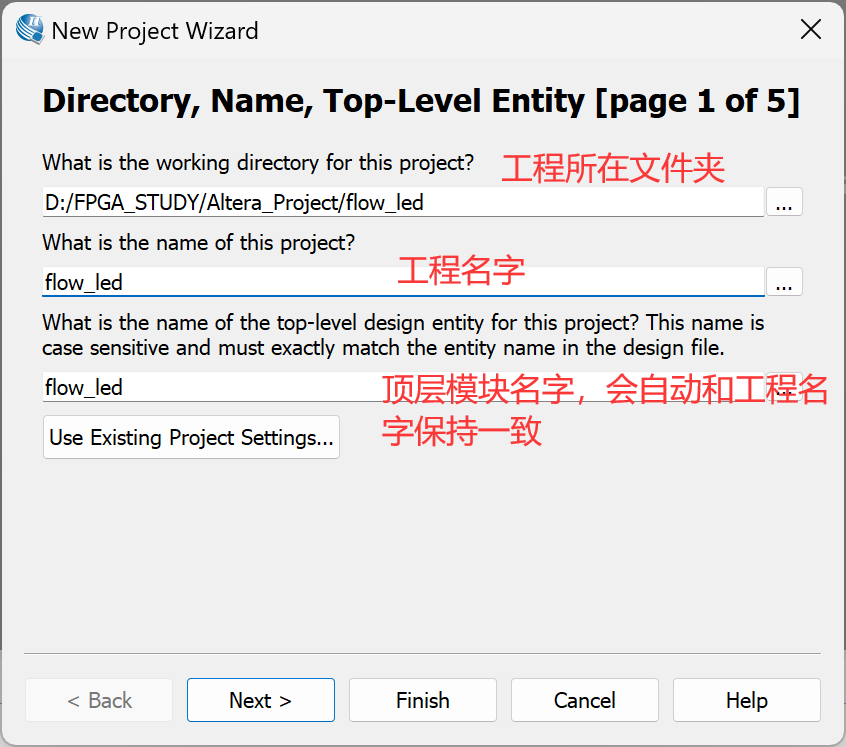

接下来我以流水灯为例,做一个演示。

点击next,进行下一步

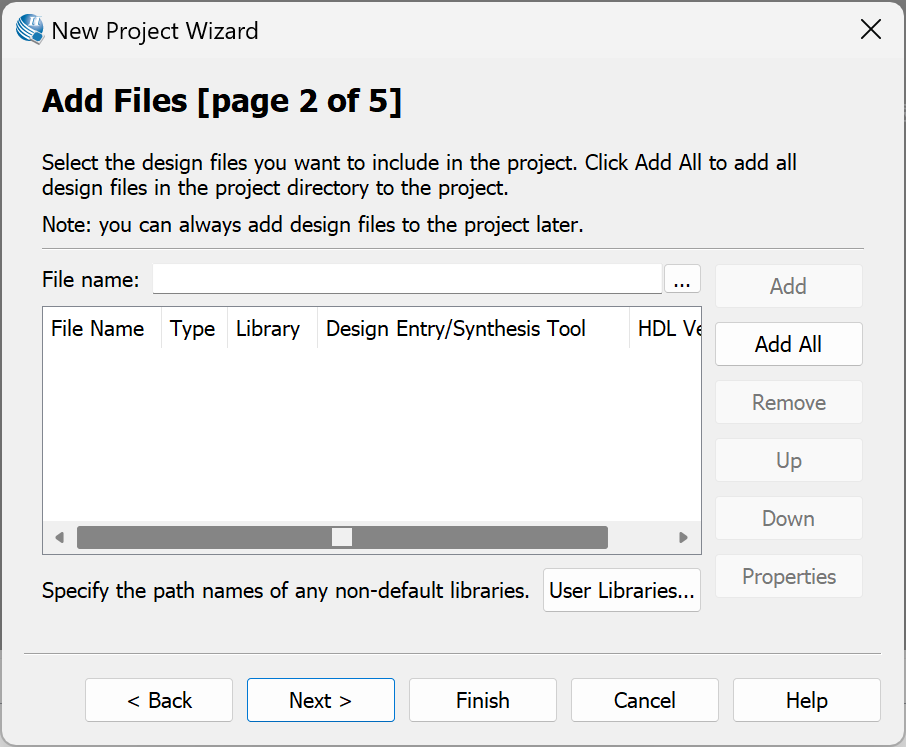

这里为添加存在的文件,如果没有的话,继续点击next

这里为添加存在的文件,如果没有的话,继续点击next

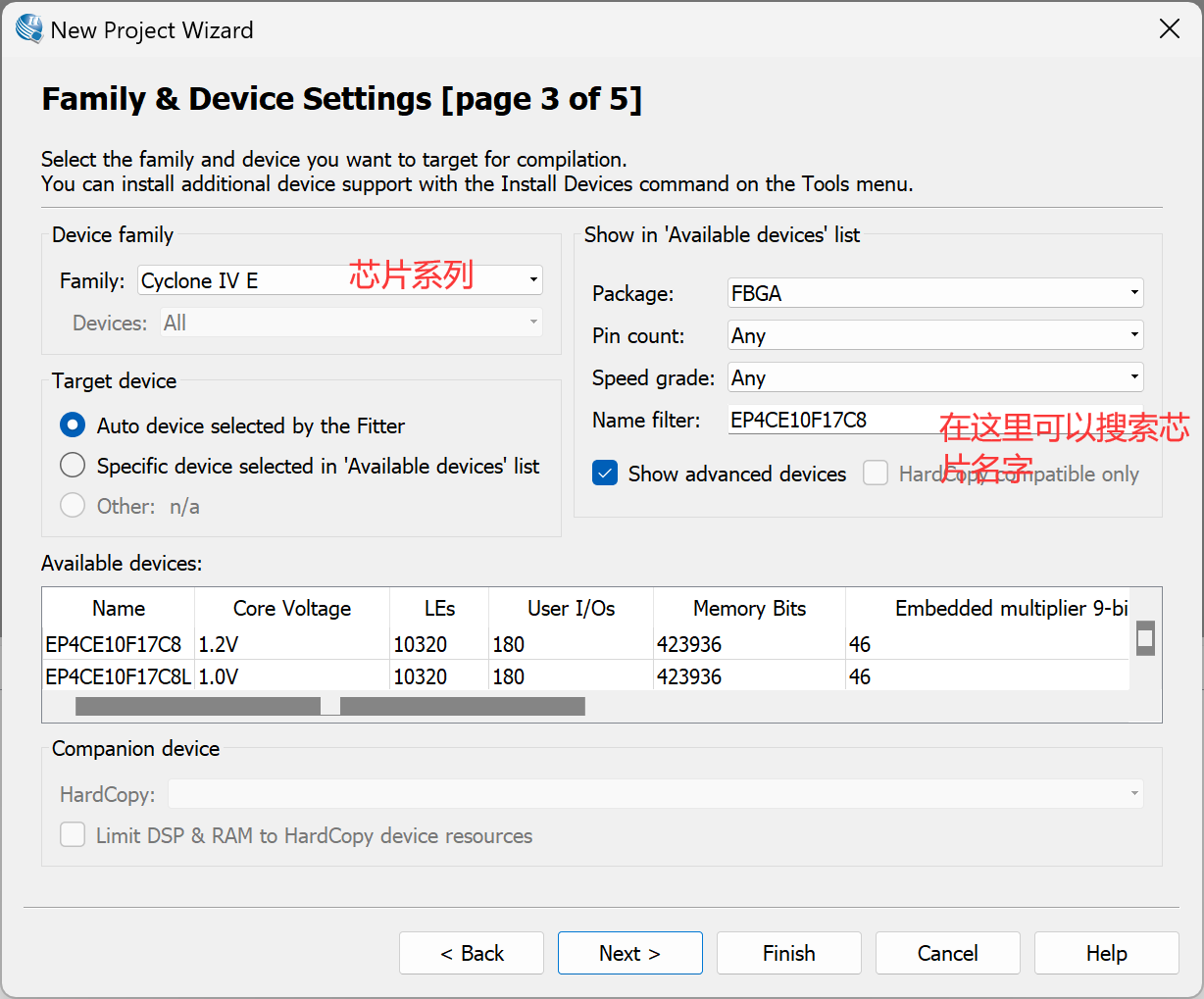

芯片名字可以在板子进行查看。继续点击next。

芯片名字可以在板子进行查看。继续点击next。

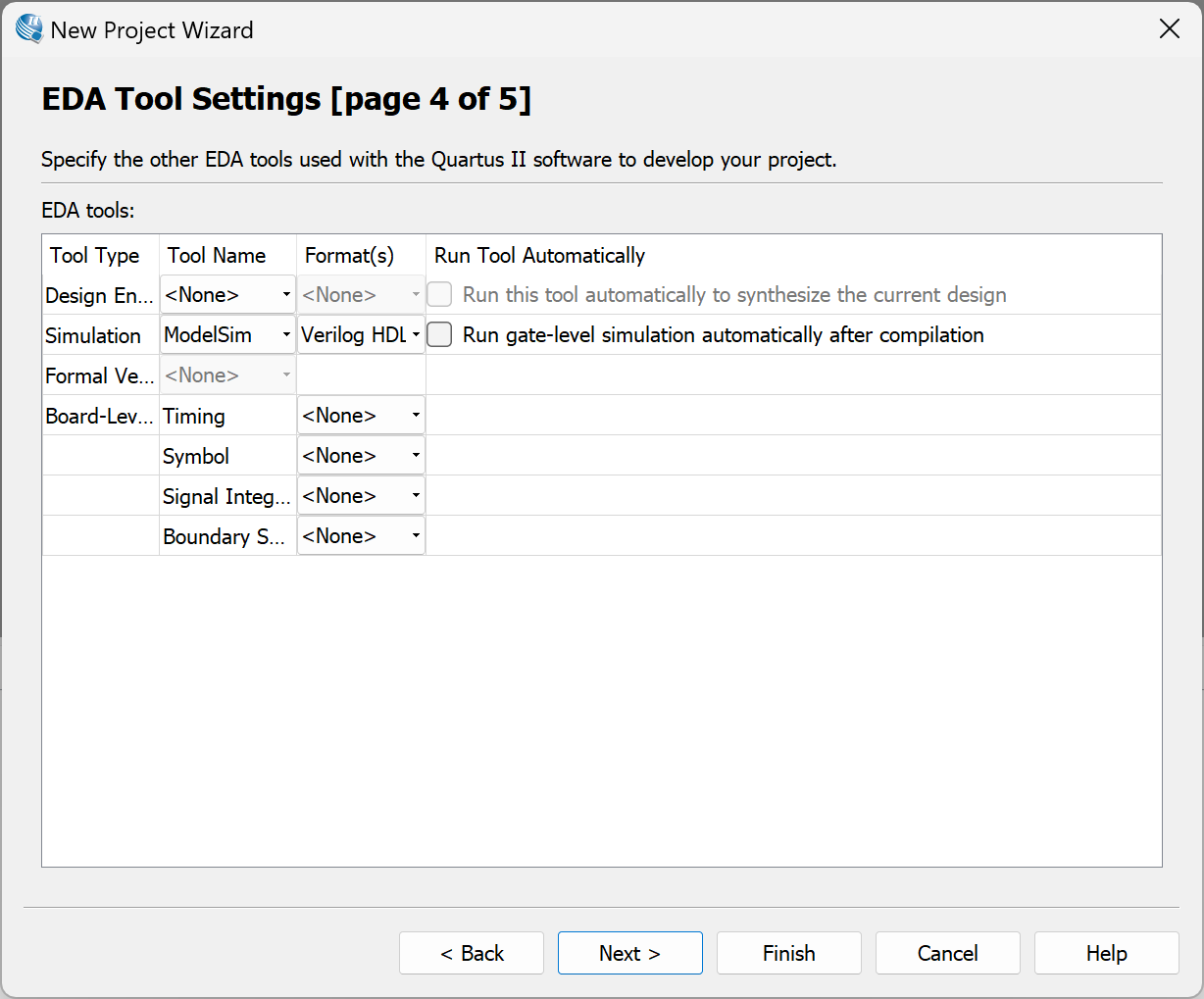

仿真工具选择modelsim,语言选择 verilog hdl,继续点击next

仿真工具选择modelsim,语言选择 verilog hdl,继续点击next

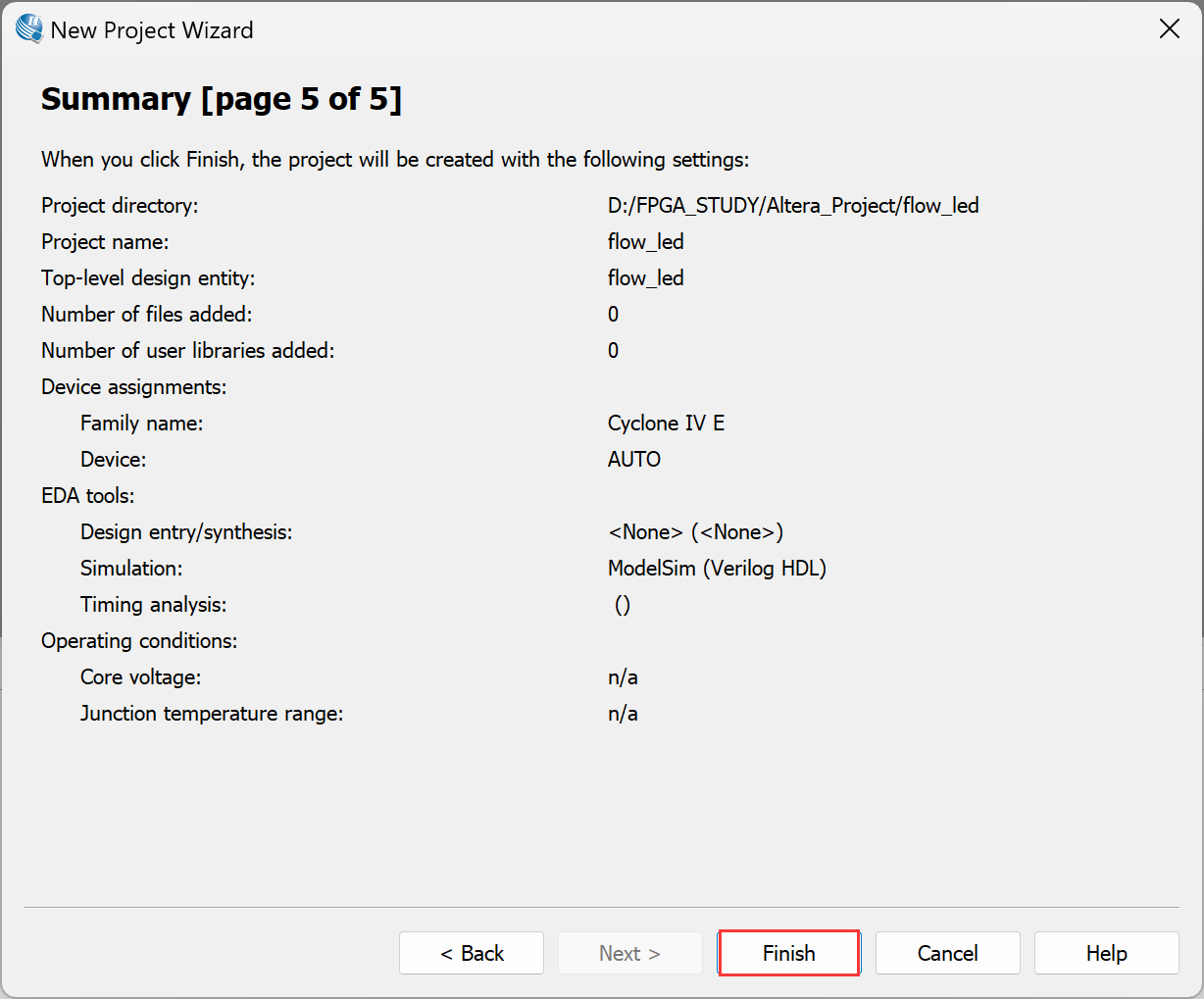

最后点击 finish,工程就建好了。

最后点击 finish,工程就建好了。

写verilog代码

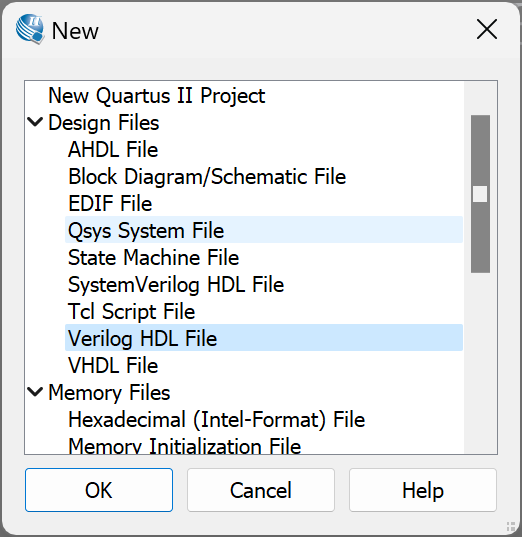

首先,点击 左上角的 File,然后点击 New,可以新建文件。或者使用快捷键 ctrl + n

选择verilog hdl file,点击ok。

选择verilog hdl file,点击ok。

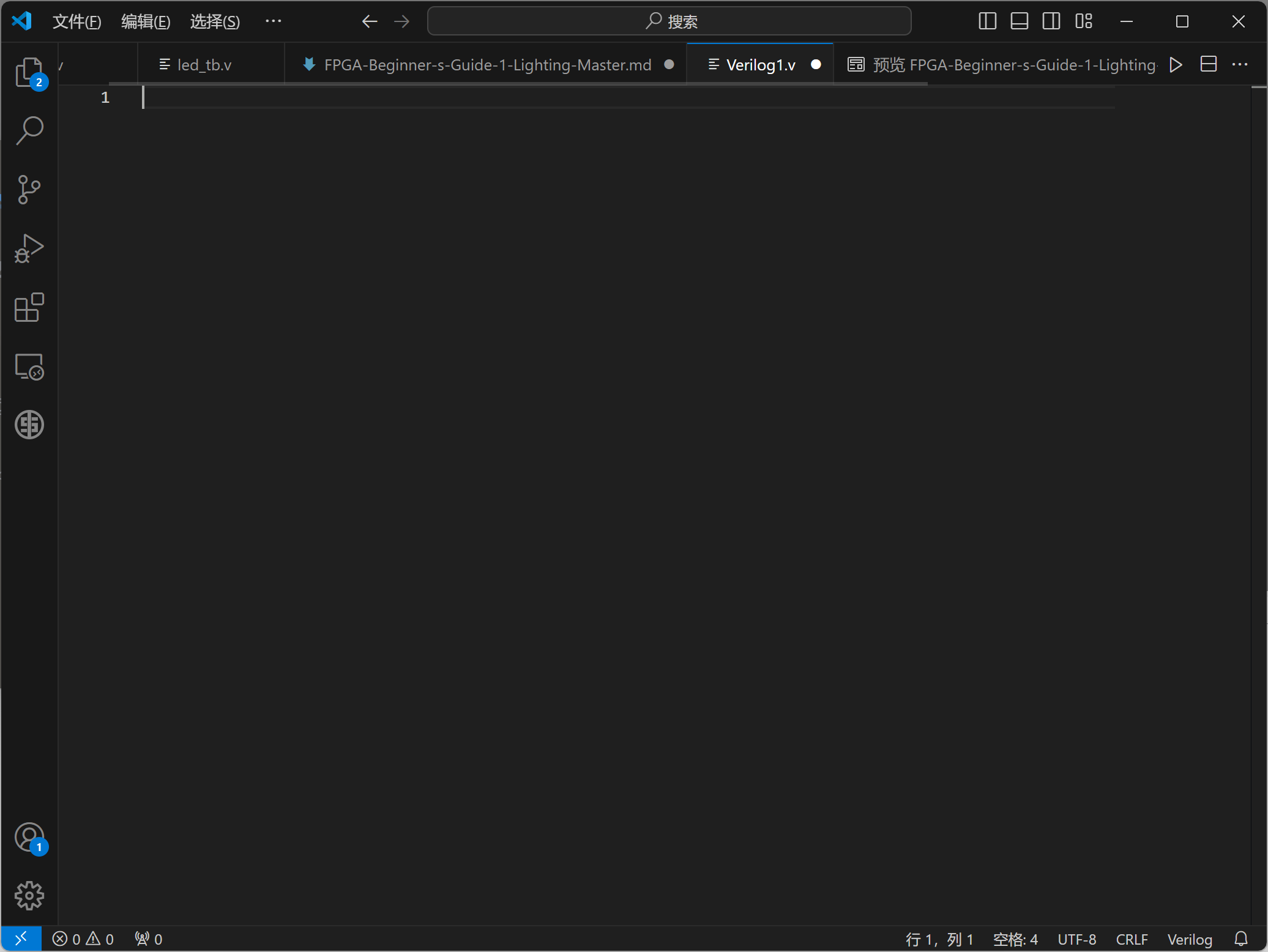

由于我的与vscode关联了,会在vscode里面显示。

由于我的与vscode关联了,会在vscode里面显示。

然后写具体代码

首先需要明确任务,这里的任务为 让led 1s闪烁一次(亮0.5s,灭0.5s)。

接下来需要设计输入。需要一个时钟,一个复位信号,还需要一个输出,当到时间了,改变输出信号。那么0.5s如何实现呢? 很简单,只需要一个计数器 [用于累计输入时钟脉冲(CP)的个数,还常用于分频、定时、产生脉冲序列和进行数字运算,是一种Moore型电路]。

需要计x个数,然后计数器清零,输出信号反转。 那么x等于多少呢?一般计数用的时钟为系统时钟50MHz,也就是 1/(5010^310^3)Hz s = 0.000_000_02s,也就是说50MHz频率的时钟一个周期的时间为0.000_000_02s。那么x应该等于 0.5 / 0.000_000_02 = 25_000_000。 由于是从0开始的,所以应该计数到24_999_999,计数器清零,且输出信号反转。

那么led.v文件内容如下

1 |

|

仿真文件如下

1 |

|

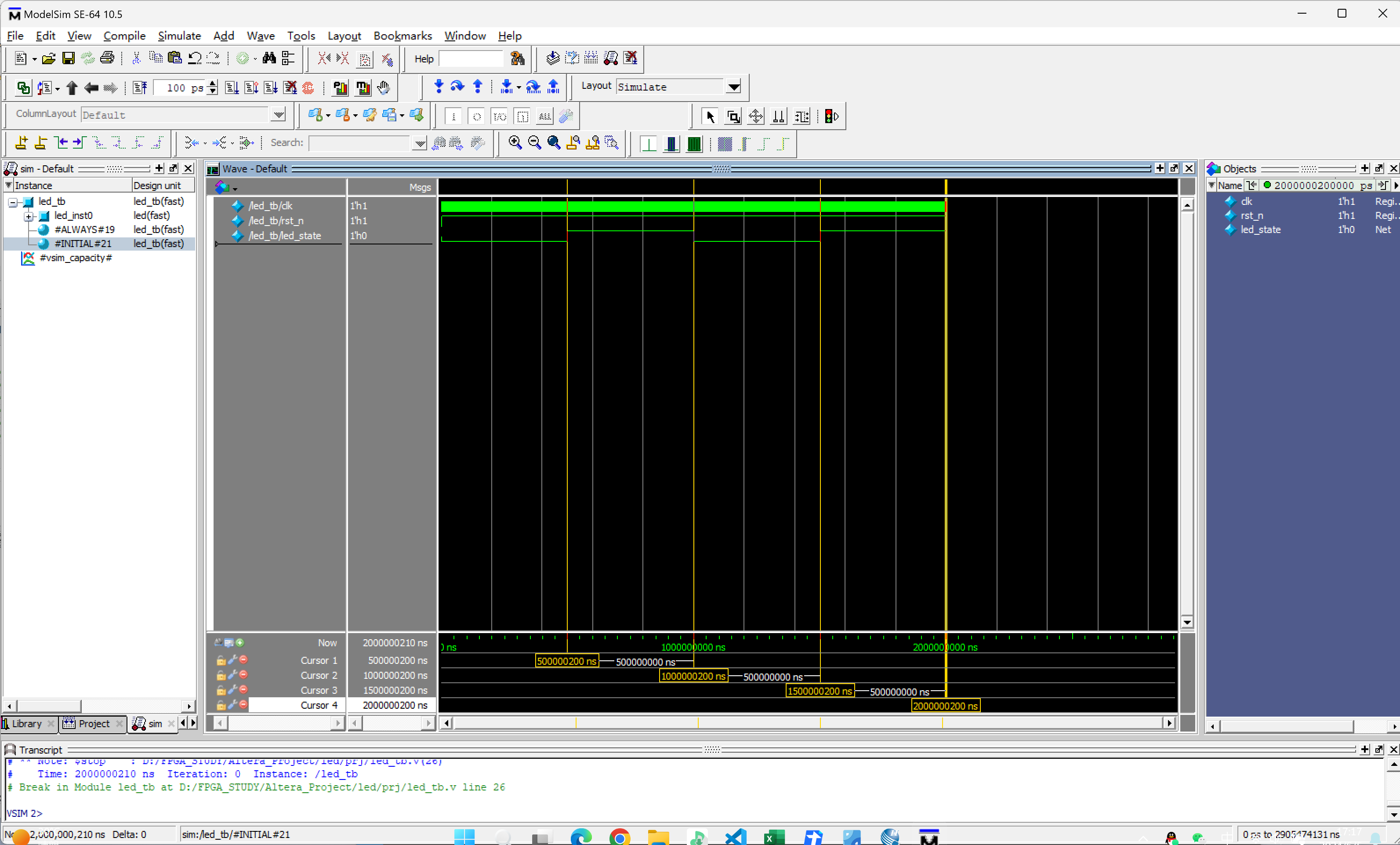

看一下仿真波形图  0.5s反转一次,没有问题。接下来就分配引脚了

0.5s反转一次,没有问题。接下来就分配引脚了

分配引脚

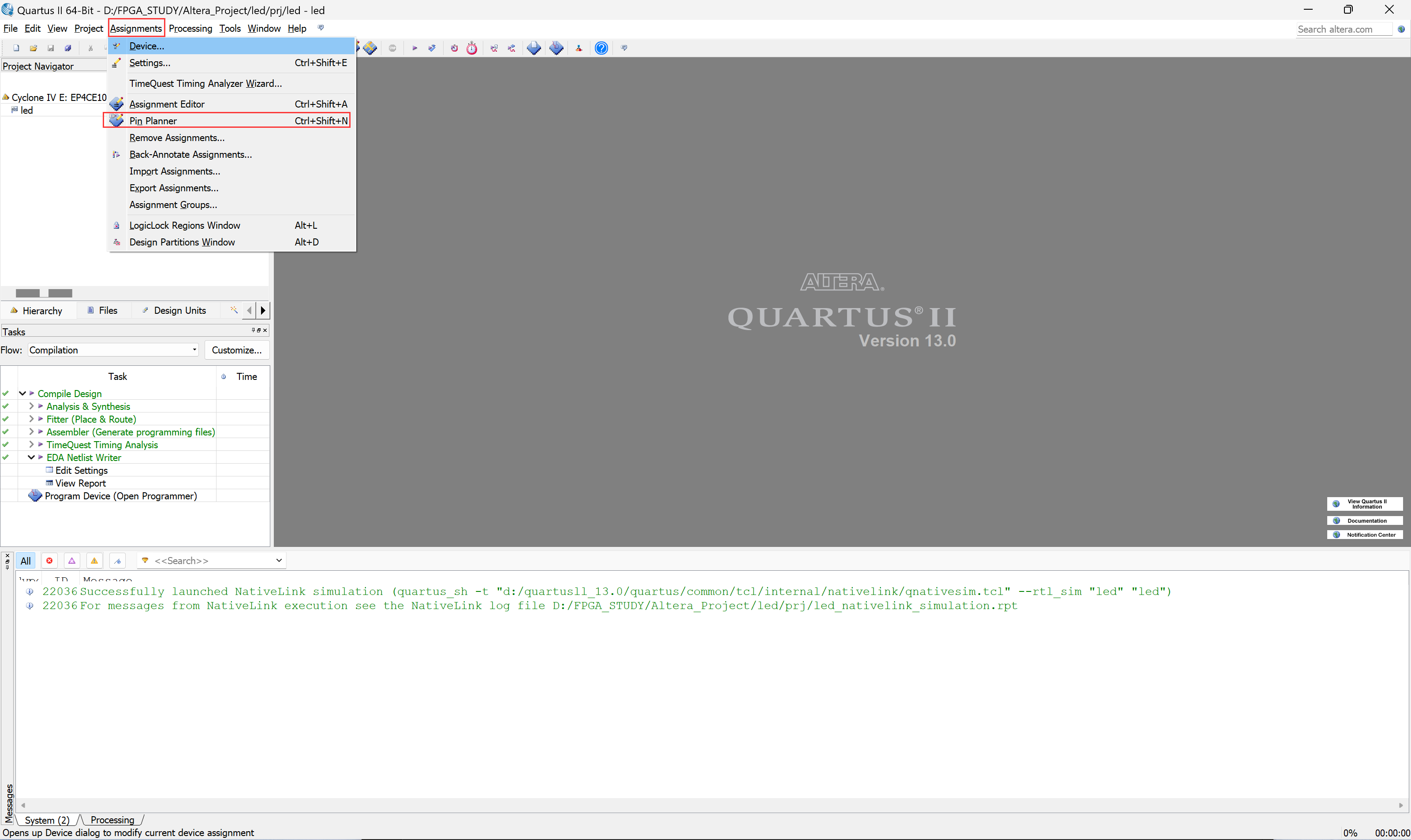

点击 Assignments,然后点击 Pin Planner

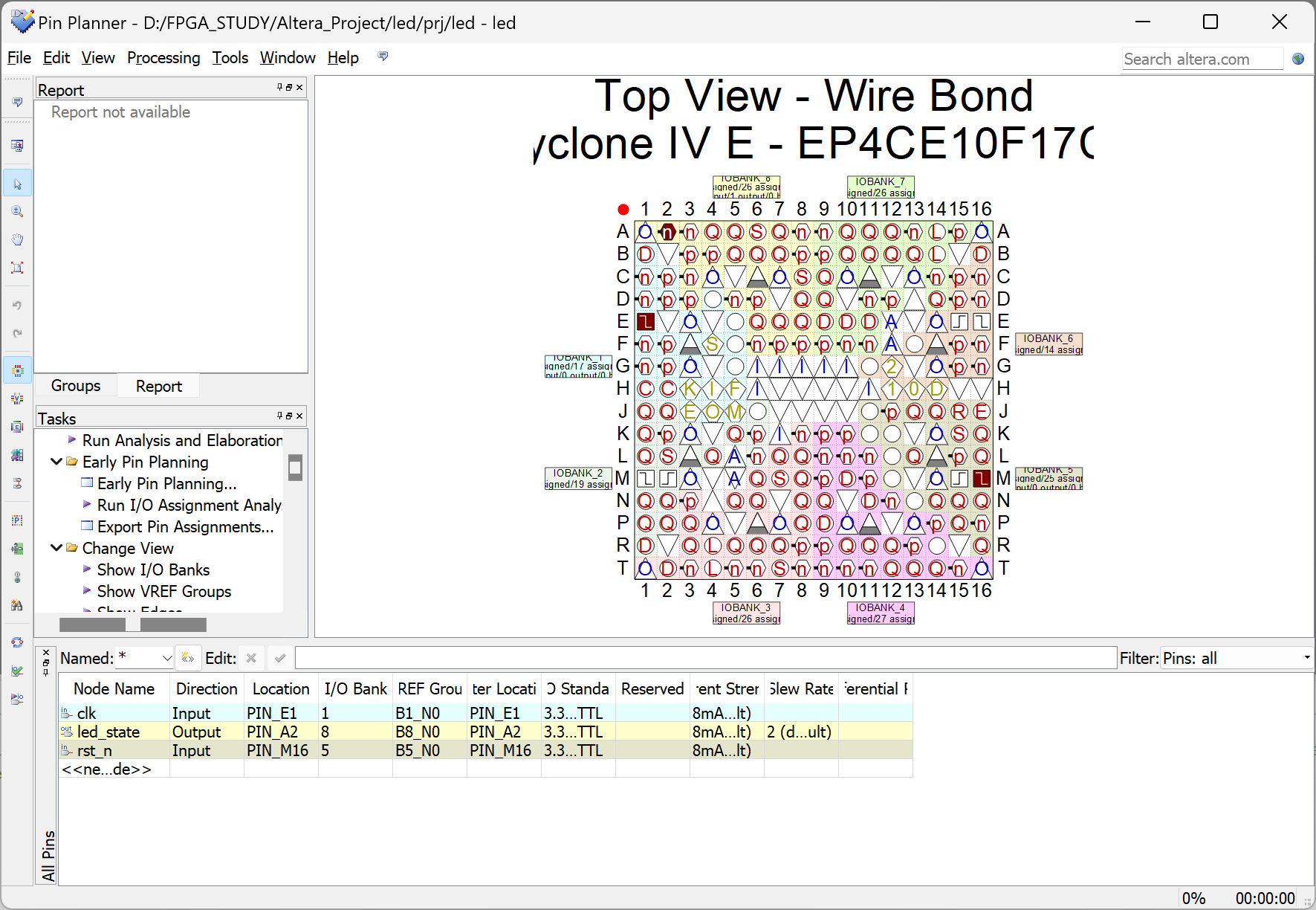

点击Location,选择每一个信号需要分配的引脚,和自己的板子资源有关。ac620的clk时钟引脚就是PIN_E1,rst_n给一个按键引脚即可,led_state给一个led灯的引脚。

点击Location,选择每一个信号需要分配的引脚,和自己的板子资源有关。ac620的clk时钟引脚就是PIN_E1,rst_n给一个按键引脚即可,led_state给一个led灯的引脚。

电平选择3.3V,这样就分配完成了。再次编译。

烧录

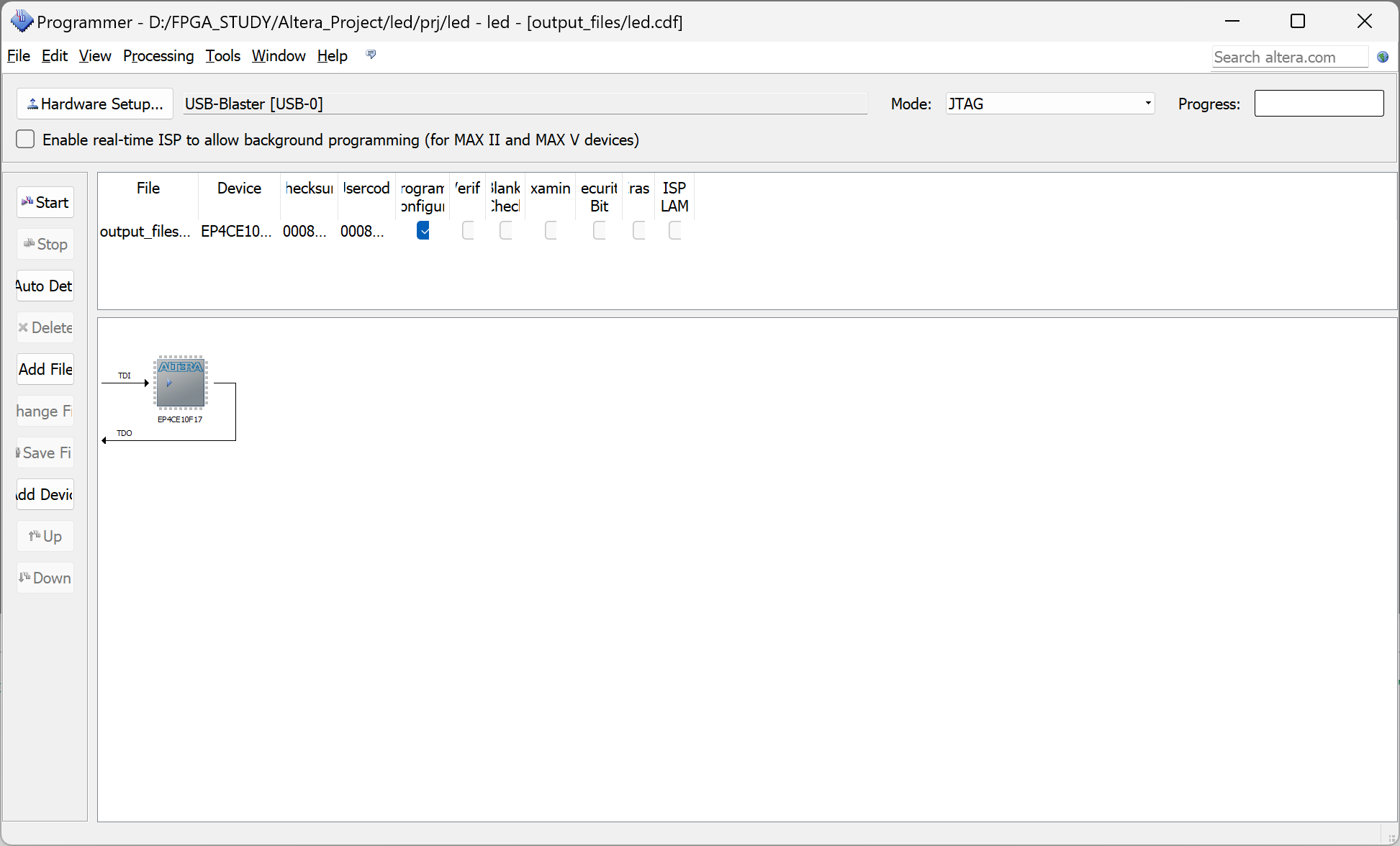

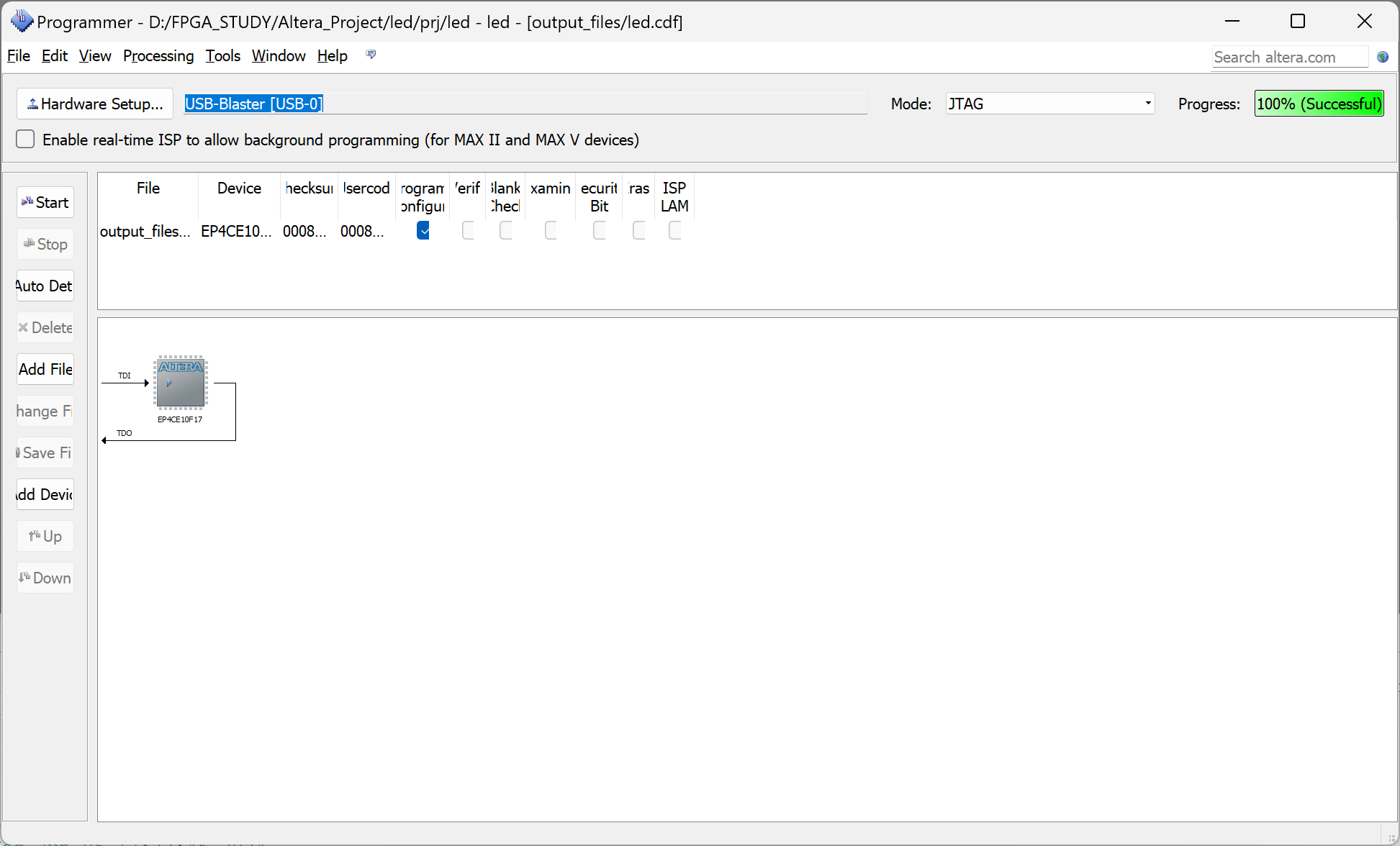

点击 program Device,会弹出下面页面

如果 file为空,则点击Add file,添加sof文件即可。

最后点击start,即可烧录,烧录成功后会显示100%(Successful)

请看最终效果,我把mp4转换为gif了。

流水灯

任务:4个led 分别开始闪烁。每次只闪烁一个led。每一次闪烁0.5s(0.25亮、0.25s灭),也就是所谓的流水灯。 就是在前面的基础上,加了一个译码器。在译码器工作时,无论输入什么,有且只有一个输出端电平与其他输出端不同。也就是只有一个端口为高电平,剩下的都为低电平。

1 | module flow_led ( |

仿真文件

1 |

|

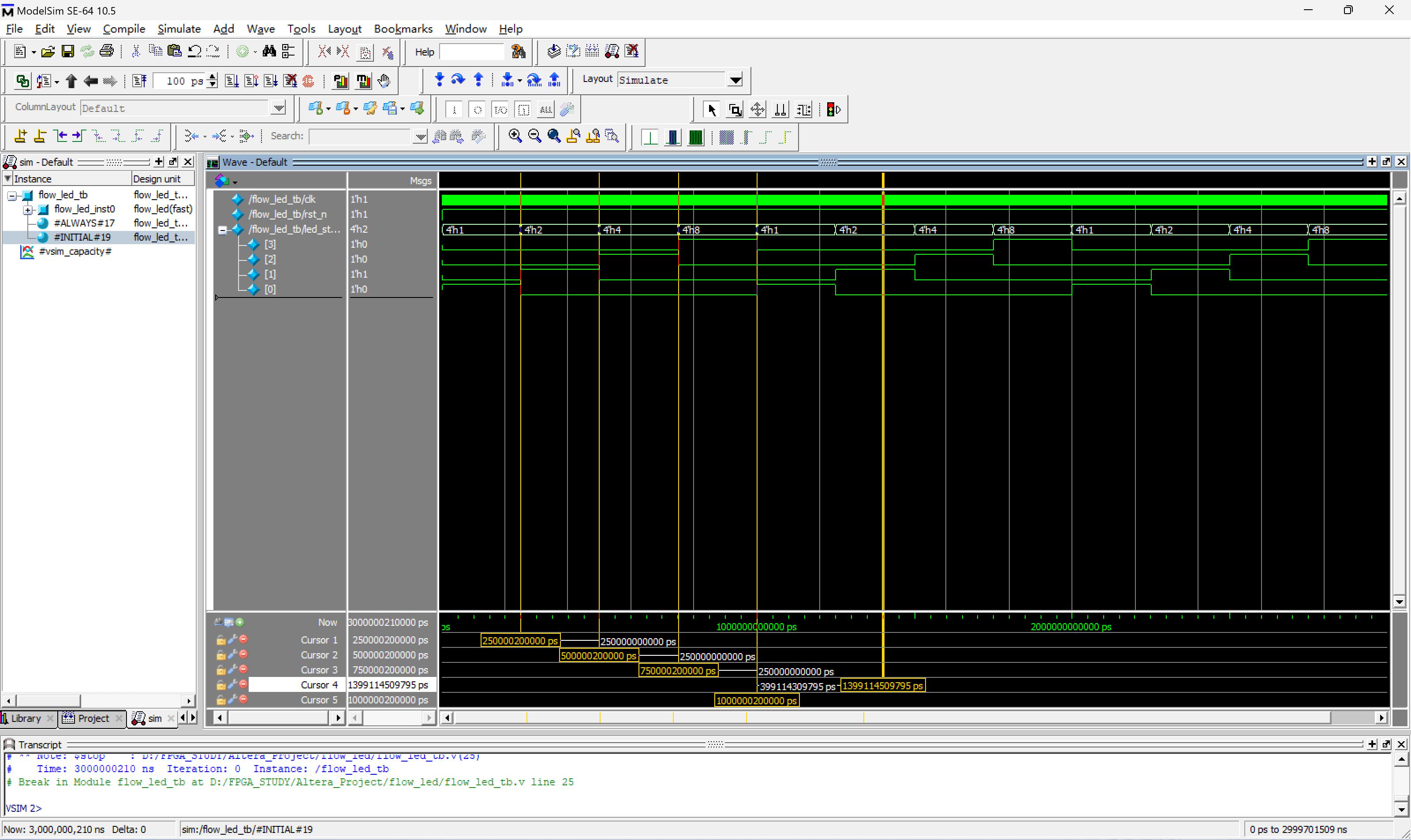

仿真波形

fa

- Title: FPGA入门教程(1):点灯大师

- Author: StarHui

- Created at : 2024-06-05 15:22:32

- Updated at : 2024-06-06 22:12:24

- Link: https://renyuhui0415.github.io/post/FPGA_Beginner's_Guide(1)_Lighting_Master.html

- License: This work is licensed under CC BY-NC-SA 4.0.